# **GaN channel Nanoscale MOSFET with Silicon Source and Drain and Silicon Germanium Bulk**

Basab Das

Dept. of Electronics & Communication Engineering

Girijananda Choudhury Institute of Management and Technology, Guwahati, India

basab\_ece@gimt-guwahati.ac.in

**Available online at: [www.ijcseonline.org](http://www.ijcseonline.org)**

**Abstract**—Extensive scaling in Conventional MOSFETs lead to degradation to their electrical parameters. This work proposes a GaN channel Nanoscale MOSFET for improvement in Electron Mobility, Off current with satisfactory On current, Threshold voltage and Subthreshold Swing Off current of the order of  $10^{-11}$  A/um and Electron Mobility of around  $1300 \text{ cm}^2/\text{V}\cdot\text{s}$  are obtained.

**Index Terms**—MOSFET, GaN, Silicon Germanium, On-Off current ratio, mobility

## INTRODUCTION

High speed device and high drain current at low supply voltage is need of present day advancement of semiconductor technology. In MOSFETs, low mobility and high off state leakage current is matter of concern in comparison to advanced device like High Electron Mobility Transistors (HEMTs). Group III-V [1] compound semiconductors are an efficient replacement as a channel material for silicon in conventional MOSFET to improve high drive current for fast switching at low off state leakage current. Various structures has been already proposed for improvement of conventional MOSFETs such as MOSFETs [2], DG MOSFETs [3], Junctionless DG MOSFETs [4], stacked high-k MOSFETs [5], Quantum-Well MOSFETs[6], Heterostructure and Silicon Double Gate Mosfet[7] and GaN MOSFET[8].

Moreover, in present day world requirement of high speed Nanoscale devices are needs, so mobility improvement must be taken care off. In this paper, we have proposed a new architecture of MOSFET, which improves off state leakage current along with mobility. Our model consists of group III-V compound semiconductor Gallium Nitride (GaN) as a replacement for silicon as channel and Silicon Germanium (SiGe) as substrate is used. In this work, we have varied gate dielectric and studied the various parameters for our architecture like electron mobility,  $I_{ON}/I_{OFF}$  ratio, threshold voltage and subthreshold swing. An accelerated mobility with excellent  $I_{ON}/I_{OFF}$  ratio is obtained.

The second section of this paper describes the structure and the third section discusses the simulation results obtained.

## DEVICE ARCHITECTURE

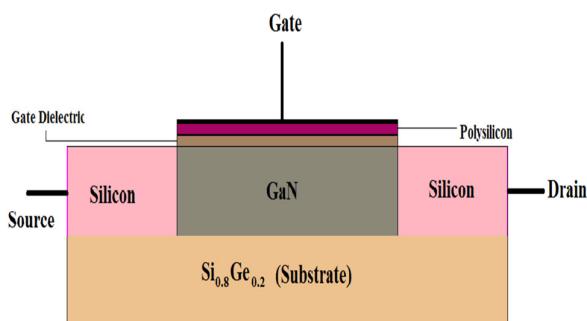

The proposed structure of the MOSFET is shown in Fig. 1. Here, GaN is used as a channel with doping concentration  $1 \times 10^{17} \text{ cm}^{-3}$  and SiGe as substrate with doping concentration  $1 \times 10^{18}$  and 20% Germanium concentration. Boron is used as dopant for channel and substrate. Source and drain is silicon region which are

doped with n-type dopant Phosphorus and doping concentration  $2 \times 10^{18}$ . Total length of the device is 120nm. The body thickness is 30nm with gate length fixed for our study at 60nm. Gate metal used here is Polysilicon and gate dielectric which are of 2nm thick.

## RESULTS AND DISCUSSION

The Sentaurus TCAD is used to simulate proposed structure. The models used are

- a) Fermi-Dirac statistics for presence of high doping.

- b) E-HighFieldSaturation, Dopingdependence and phumob as Mobility models.

- c) SRH (Dopingdependence) as Recombination models.

Our study has been done using three gate dielectrics which are Silicon Dioxide ( $k = 3.9$ ), Alumina ( $k = 10$ ) and Hafnium Oxide ( $k = 22$ ) where  $k$  is the dielectric constant.

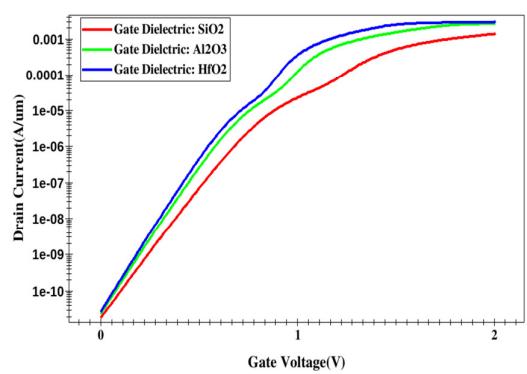

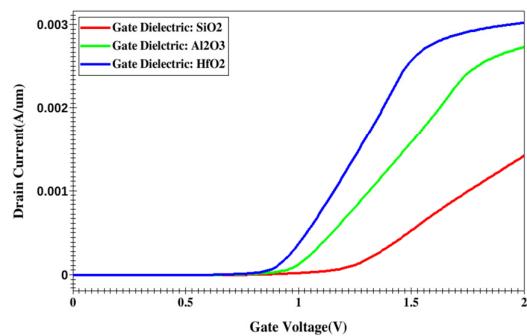

The linear plot of drain current versus gate voltage for different gate dielectrics is shown in Fig. 2 and logarithmic plot has been shown in Fig. 3. Simulation is done for  $V_{DS}=0.5\text{V}$  and gate voltage is ramped from 0 to 2 V. We observe that  $I_{ON}/I_{OFF}$  increases with increase in value of gate dielectric constant increases. Here, highest on current is obtained for  $\text{HfO}_2$  and value is  $3.026\text{mA}/\mu\text{m}$ . The capacitance is directly proportional to dielectric constant, as a result at higher value of dielectric constant ( $k$ ), more channel inversion is obtained which is depicted by Eq. 1.

$$C = (k\epsilon_0 A)/t_{ox} \quad (1)$$

Where,  $C$  is the capacitance,  $k$  is the dielectric constant,  $\epsilon_0$  is the permittivity of vacuum,  $A$  is the area of the gate and  $t_{ox}$  is the gate oxide thickness.

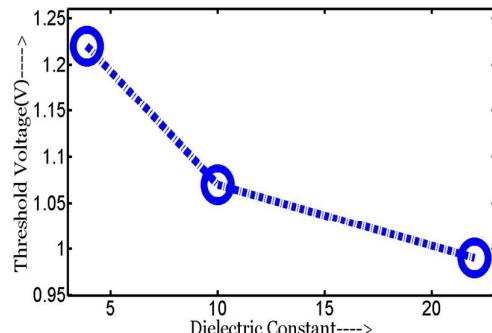

The variation of threshold voltage reduces for increase in dielectric constant as shown in Fig.4. Reason is well explained Eq. 1. Increase of dielectric constant increases capacitance, as a result we get inversion of channel at lower gate voltage. The threshold voltage reduces to 0.99V for  $\text{HfO}_2$  as gate dielectric from 1.22V for  $\text{SiO}_2$  as gate dielectric. The best result for our structure is for  $\text{HfO}_2$  as gate dielectric.

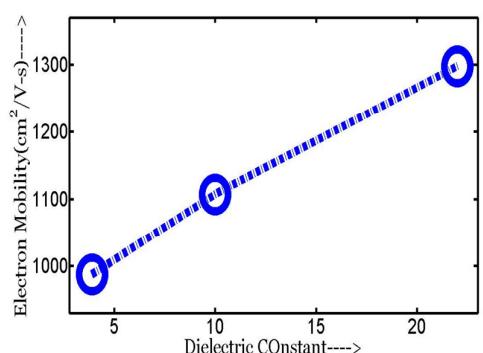

Fig. 5 shows the variation of electron mobility with dielectric constant and it is observed that, electron mobility increases as value of dielectric constant increases. Where, highest value for electron mobility is obtained for  $\text{HfO}_2$  as  $1.298 \times 10^3 \text{ cm}^2/\text{V}\cdot\text{s}$ .

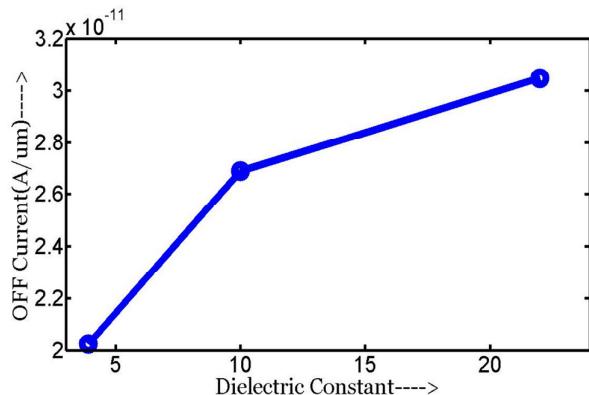

Fig. 6 shows value of off current for different dielectrics, it is observed that off current increases as  $K$  increases, which is well explained as threshold voltage reduces results in increase in off current.  $\text{SiO}_2$  as gate dielectric gives the lowest off current, value is  $2.024 \times 10^{-11} \text{ A}/\mu\text{m}$ .

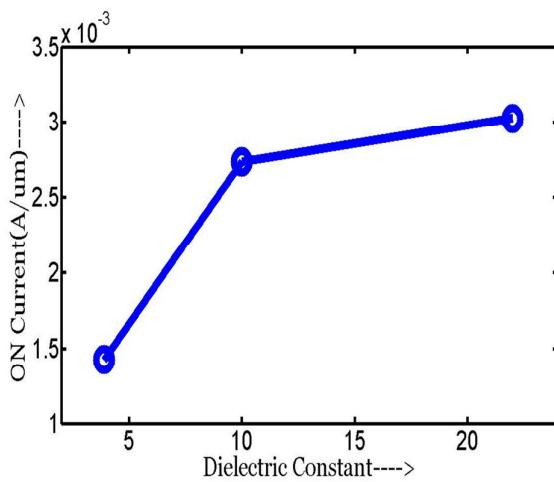

Fig. 7 shows plot of on current for different dielectrics. Highest on-current is obtained is  $3.026 \times 10^{-3} \text{ A}/\mu\text{m}$  for  $\text{HfO}_2$  as gate dielectric.

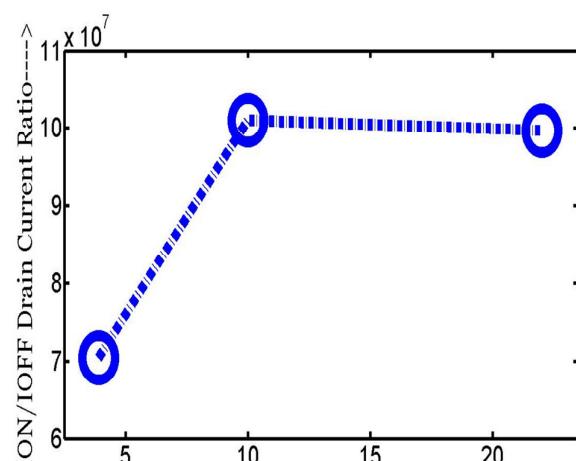

Fig. 8 shows plot of  $I_{\text{on}}/I_{\text{off}}$  ratio. An excellent value of  $10^8$  is achieved for  $k = 22$ . Moreover, for the other two cases too, the ratios are greater than  $10^6$ .

Fig.9 shows plot of subthreshold swing versus variation of dielectric constant, Subthreshold Swing (SS) of a device is a measure of how well the device switches off. We observed subthreshold swing reduces with increase in gate dielectric. Whereas, SS of a MOSFET is limited to 60 mV/dec as subthreshold drain current depends on thermal voltage ( $kT/q$ ). Generally, MOSFETs have SS in the range of 100 – 200 mV/dec. In this work, we have obtained low values of SS for  $\text{HfO}_2$  as gate dielectric of the value 117.23 mV/dec.

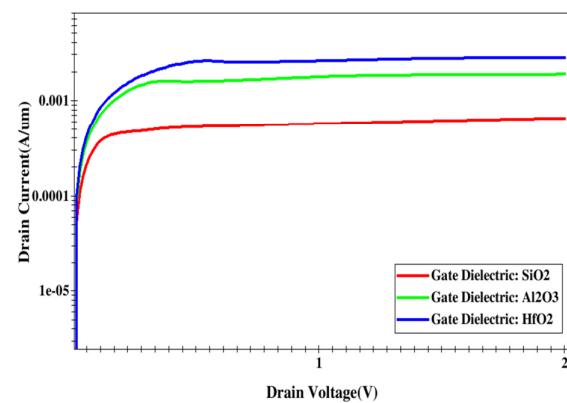

The plot of  $I_D$ - $V_{\text{DS}}$  for different dielectrics is shown in Fig. 10 for  $V_{\text{GS}}$  equal to 1.5 V.

### CONCLUSION

The proposed MOSFET structure in this work has very promising outcome for the semiconductor world. The  $I_{\text{on}}/I_{\text{off}}$  ratio is satisfactorily improved along with high on-current and electron mobility, which make this device useful for digital application. The best suited observed gate dielectric for proposed structure is  $\text{HfO}_2$ . The scope of this work may be extended to improving the SS without degrading the on-current and electron mobility.

2D structure of the proposed MOSFET

Linear plot of Drain Current versus Gate Voltage for fixed drain voltage at 0.5 V.

Logarithmic plot Drain Current versus Gate Voltage for fixed drain voltage of 0.5V.

Threshold Voltage variation with various Gate Dielectric constant (K) at drain voltage of 0.5 V

Electron Mobility variation with various Gate Dielectric Constant (K) at drain voltage of 0.5V.

OFF current variation with various Gate Dielectric Constant(K) at drain voltage of 0.5 V

Subthreshold Swing variation with various Gate Dielectric constant(K) at drain voltage of 0.5 V

ON current variation with various Gate Dielectric constant(K) at drain voltage of 0.5 V

Drain Current versus Drain Voltage plot for different gate dielectric constants for Gate Voltage of 1.5 V

## REFERENCES

- [1]. U. K. Mishra, Y.Wu, B. P. Keller, S. Keller and S. P. Denbaars, "GaN Microwave Electronics", IEEE Trans. on Microwave Theory and Techniques, vol. 46, no.6, pp. 756-761, June 1998.

- [2]. G. Mahajan, V. K. Chaubey, R. Narang and M. Saxena, "Mixed mode Circuit Simulation of Silicon and Germanium Nanowire MOSFETs" Proceeding of the 2011 IEEE Students' Technology Symposium, Kharagpur, pp. 292-296

- [3]. R. Prasher, D. Dass and R. Vaid, " Performance of a Double Gate Nanoscale MOSFET (DG-MOSFET) Based on Novel Channel Materials", Journal of Nano- and Electronic Physics, vol. 5, pp. 01017-1 – 01017-5, March 2013

- [4]. Z. Chen *et. al.*, "Surface-Potential-Based Drain Current Model for Long-Channel Junctionless Double-Gate MOSFETs, IEEE Transactions on Electron Devices, vol. 59, pp. 3292-3298, December 2012

- [5]. S. H. Chen *et. al.*, "High-performance III-V MOSFET with nano-stacked high-k gate

ON-OFF current ratio with various Gate Dielectric constant(K) at drain voltage of 0.5 V

dielectric and 3D fin-shaped structure”, Nanoscale Research Letters, vol. 7, pp. 1-5, December, 2012

[6]. A. Ali *et.al* ,” Enhancement-Mode Antimonide Quantum-Well MOSFETs with High Electron Mobility and Gigahertz Small-Signal Switching Performance”, IEEE Electron Device Letter, vol. 32, pp. 1689–1691, December 2011

[7]. S. Pati, H.Pardeshi, G. Raj, N Kumar, C. Sarkar, “Comparision study of drain current, Subthreshold Swing and DIBL of III-V Heterostruture and Silicon Double Gate MOSFET”, Internation Journal of Electronics and Communication Technology, vol. 4, pp. 33-35, January 2013.

[8]. A. M. Ozbek *et.al.*,”Projections of Schottky Barrier Source-Drain Gallium Nitride MOSFET Based on TCAD Simulation and Experimental Results”, International Semiconductor Device Research Symposium, December 2007.

#### Author Profile

**Basab Das** received his M.Tech degree in Microelectronics and VLSI Design from National Institute of Technology Silchar, Silchar, Assam, India in 2014 and B.Tech in Electronics and Communication Engineering from North Eastern Hill University, Shillong, Meghalaya, India in 2010. Since 2014, he has been an Assistant Professor in Department of Electronics and Communication Engineering, Girijananda Choudhury Institute of Management and Technology, Guwahati, India. He has 10nos. of publication in various International Journal/Conferences. His research interest includes simulation and modeling of solid state devices and Mixed Signal Circuit Design.